Sở TT&TT TP Đà Nẵng vừa cho biết khóa học dự kiến kéo dài 6 tháng (3 tháng học lý thuyết và thực hành, 3 tháng làm dự án).

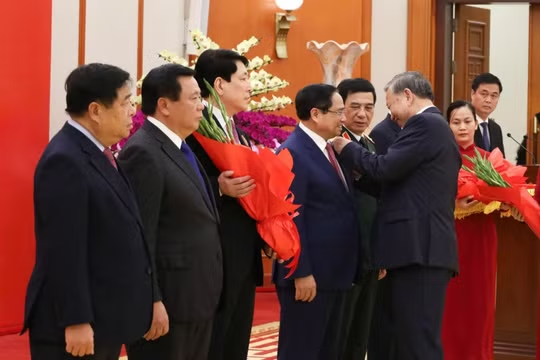

“Đây là khoá học đầu tiên, trong khuôn khổ chương trình đào tạo theo nội dung biên bản hợp tác giữa UBND TP Đà Nẵng với Tập đoàn Synopsys và biên bản hợp tác giữa Trung tâm Nghiên cứu, đào tạo thiết kế vi mạch và trí tuệ nhân tạo Đà Nẵng (Trung tâm DSAC) với Tập đoàn Synopsys”, Ông Lê Hoàng Phúc - Giám đốc Trung tâm DSAC – cho biết.

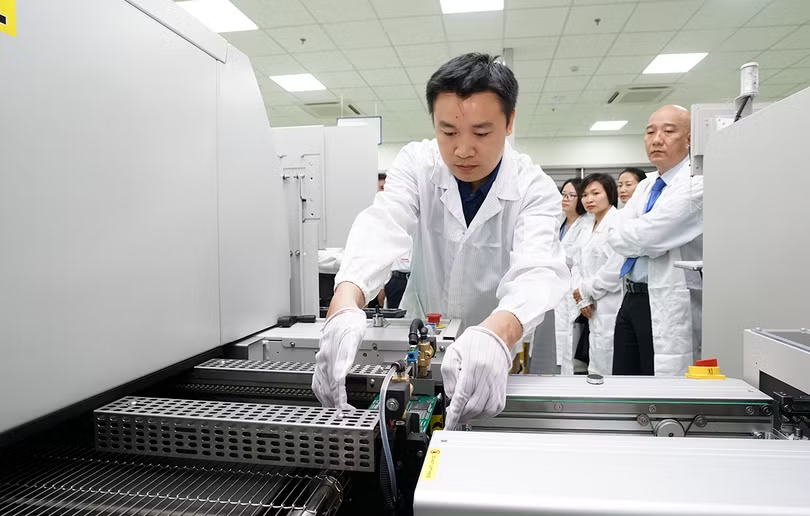

Nội dung chương trình bồi dưỡng do Đại học Công nghệ Đại học Việt - Hàn, Viện CNTT Đại học Quốc gia Hà Nội và Tập đoàn Synopsys xây dựng. Học viên sẽ học lý thuyết và thực hành (dự kiến 3 tháng) tại Trung tâm Vi mạch và Công nghệ thông minh, Trường Đại học CNTT và Truyền thông Việt – Hàn, Đại học Đà Nẵng; thực hành dự án (dự kiến 3 tháng) tại doanh nghiệp thiết kế vi mạch.

Các học viên sẽ tham gia qua 4 khoá học gồm: Khoá 1-VLLSI Design (thời lượng 15 giờ học) với nội dung giới thiệu về thiết kế có mật độ tích hợp cao, giới thiệu về các công nghệ bán dẫn, thiết kế hệ thống và phát triển ứng dụng, thiết kế số, thiết kế analog và thiết kế hỗn hợp và đánh giá cuối khóa học;

Khoá học 2 - Basic Digital Design & Hardware Description Language (SystemVerilog/Verilog/VHDL) có thời lượng 48 giờ học, với các nội dung: Hệ thống số & đại số bool, các phần tử cơ bản của mạch điện số, nguyên lý thiết kế mạch Logic tổ hợp, ngôn ngữ miêu tả phần cứng, thực hành mô phỏng mạch số dùng ngôn ngữ miêu tả phần cứng, miêu tả các hàm logic tổ hợp và phần tử mạch cơ bản dùng ngôn ngữ miêu tả phần cứng, thực hành thiết kế mạch logic tổ hợp dùng ngôn ngữ miêu tả phần cứng, nguyên lý thiết kế mạch tuần tự & máy trạng thái, thiết kế mạch tuần tự và máy trạng thái sử dụng Ngôn ngữ miêu tả phần cứng, thực hành thiết kế mạch logic tuần tự và máy trạng thái và bài tập cuối khóa;

Khóa học 3 - Thực thi mạch tích hợp số cơ bản, có thời lượng 54 giờ học, với các nội dung: Synthesis và các kỹ thuật tối ưu, thực hành tổng hợp phần cứng, chip Input/Output & Floorplan, thực hành Floorplan và chip I/O, Place & route, thực hành định tuyến và đặt chỗ, Static Timing analysis, thực hành STA, Post-synthesis/post-PNR simulation và bài tập cuối khóa;

Khóa học 4 - Thiết kế mạch tương tự cơ bản có thời lượng 54 giờ học, bao gồm các nội dung: Giới thiệu về công nghệ CMOS, quy trình chế tạo và mô hình thiết bị, phương pháp thiết kế và phân tích các mạch tương tự, mô phỏng mạch điện tương tự, thực hành vẽ và mô phỏng mạch điện tương tự một số mạch tương tự cơ bản, giới thiệu về luật thiết kế (DRC) trong công cụ CMOS, layout transistor và các mạch tương tự, thực hành layout mạch tương tự, layout-versus-schematic + thực hành, parasitic extraction + thực hành, mô phỏng sau khi trích xuất phần tử ký sinh, và bài tập cuối khóa.

“Việc triển khai bồi dưỡng giảng viên thiết kế vi mạch là một trong những nhiệm vụ quan trọng trong thực hiện chủ trương phát triển nguồn nhân lực lĩnh vực công nghiệp vi mạch, bán dẫn của TP Đà Nẵng trong thời gian tới. Trên cơ sở kết quả đào tạo giảng viên khóa I này, Trung tâm DSAC sẽ tham mưu lựa chọn những giảng viên tiêu biểu để báo cáo cấp có thẩm quyền cho phép cử tham gia các lớp tập huấn nâng cao trong và ngoài nước để nâng cao trình độ đội ngũ giảng viên thiết kế vi mạch, bán dẫn”, Giám đốc Trung tâm DSAC cho hay.